Типы и логическое устройство процессоров и оперативной памяти

Процессоры.

Материнская плата — это самое большое и сложное устройство. Материнская плата — сложная многослойная печатная плата, являющаяся основой построения вычислительной системы (компьютера). Чтобы все устройства на материнской плате функционировали, на материнской плате имеется разъем для подключения блока питания. Именно к материнской плате подключаются все другие устройства, входящие в состав системного блока. Она обеспечивает связь между всеми устройствами ПК, посредством передачи сигнала от одного устройства к другому. На материнской плате имеется большое количество разъемов, предназначенных для установки других устройств: socket (сокет)– гнездо для процессора, slots (слоты) – разъемы под оперативную память и платы расширения, а также портов для подключения устройств ввода-вывода. Поэтому при выборе материнской платы стоит внимательно изучить все ее разъемы и порты и понять подходит ли она вам или нет.

И наверно, самым важным устройством, которое подключается к материнской плате, является процессор.

Процессор – устройство, выполняющее арифметические и логические операции, и управляющее другими устройствами компьютера. В его состав входят:

- арифметико-логическое устройство (АЛУ);

- устройство управления (УУ);

- регистры;

Современные процессоры работают согласно принципам машины фон Неймана (архитектуре фон Неймана).

Мощность процессора измеряется в его тактовой частоте. Тактовая частота–количество элементарных операций (тактов) за 1 секунду и измеряется в [Hz, MHz, GHz]. При выборе процессора нужно обратить внимание на тактовую частоту внутренней и внешней шины, на кэш- память и на количество ядер. Кроме того, разъемы процессоров (сокеты) даже одной фирмы-производителя могут отличаться.

Чтобы процессор не перегревался, у него имеется собственная система охлаждения. Она используется для отвода тепла от нагревающегося процессора. Чаще используется воздушное охлаждение с помощью кулера (вентилятор + радиатор). Радиатор выполнен из алюминия для лучшей передачи тепла от процессора. Между процессором и радиатором находится тонкий слой термопасты, чтобы исключить воздушную прослойку для лучшей теплопроводности.

Центральный процессор (ЦП) – это основное устройство ЭВМ, осуществляющее обработку данных и выполняющее функции управления системой (инициирование ввода/вывода, управление доступом к основной памяти, обработку сигналов, поступающих от различных внешних устройств и от внутренних устройств ЭВМ и др.).

1. Логическая структура цп.

Организация центрального процессора (ЦП) определяется архитектурой и принципами работы ЭВМ (состав и форматы команд, представление чисел, способы адресации, общая организация машины и её основные элементы), а также технико-экономическими показателями.

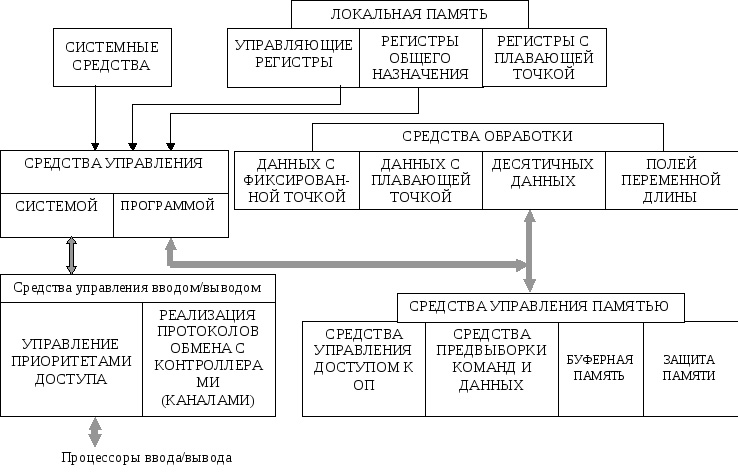

Рис. 1. Логическая структура ЦП

Логическую структуру ЦП представляет ряд функциональных средств (см. рис. 1.):

-

- средства обработки;

- средства управления системой и программами;

- локальная память;

- средства управления вводом/выводом и памятью;

- системные средства.

Средства обработки обеспечивают выполнение операций с числами с фиксированной точкой, с числами с плавающей точкой, с десятичными данными и с полями переменной длины.

Локальная память состоит из регистров общего назначения, регистров с плавающей точкой, а также управляющих регистров.

Средства управления памятью подразделяются на средства управления доступом к ОП, средства предварительной выборки команд и данных, буферную память и средства защиты памяти.

Средства управления вводом/выводом обеспечивают приоритетный доступ программ к периферийным устройствам через каналы ввода/вывода (или контроллеры).

К системным средствам относятся средства службы времени: часы астрономического времени, таймер, коммутатор и т. д.

Существует обязательный минимальный (стандартный) набор функциональных средств для каждого типа центрального процессора. Он включает в себя:

-

- регистры общего назначения;

- средства выполнения стандартного набора операций;

- средства управления вычислительным процессом.

Конкретная реализация ЦП может различаться составом средств, способом их реализации, техническими параметрами.

2. Структурная схема процессора.

Все функциональные средства по своей структуре разбиваются на следующие устройства:

- Центральное устройство управления.

- Арифметико-логическое устройство.

- Устройство управления памятью.

- Сверхоперативное запоминающее устройство.

- Устройство предварительной выборки команд и данных.

- Интерфейс магистрали.

Центральное устройство управления (ЦУУ) включает дешифратор команд, блок управления и блок прерываний.

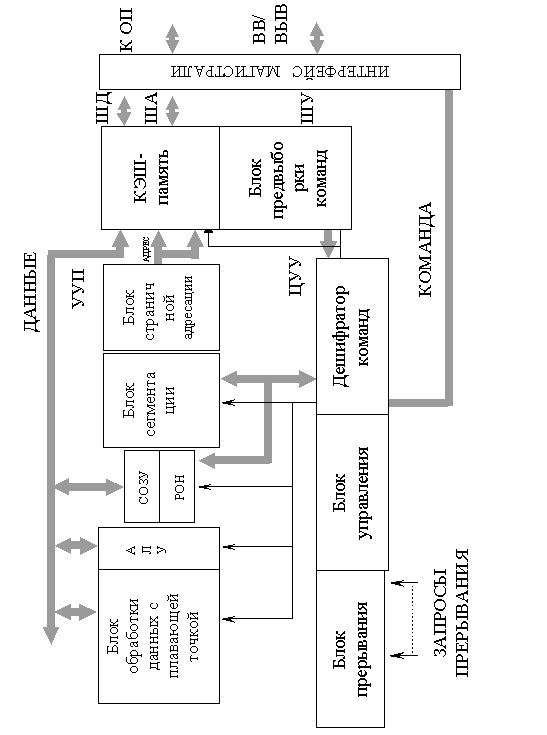

Рис. 2. Структурная схема ЦП изображена

Дешифратор команд дешифрирует (декодирует) команды, которые поступают из блока предварительной выборки.

Блок управления (БУ) формирует последовательности управляющих сигналов, которые поступают на все блоки процессора, обеспечивающие выполнение текущей команды и переход к выполнению следующей.

Блок прерывания обеспечивает реакцию ЭВМ на запросы прерываний от различных источников (устройств) внутри и вне ЦП.

Арифметико-логическое устройство (АЛУ) выполняет все арифметические и логические операции ЭВМ. В состав устройства входят:

- сумматоры;

- буферные и рабочие регистры;

- специализированные аппаратные средства (блок ускоренного умножения);

- собственный блок управления (иногда).

Во многих современных процессорах операции с плавающей точкой выполняются в отдельном блоке, который имеет собственные регистры данных, регистры управления и работает параллельно с блоком операций с фиксированной точкой.

Сверхоперативное запоминающее устройство (СОЗУ) – (регистровый файл) содержит регистры общего назначения, в которых хранятся данные и адреса.

Устройство предвыборки команд и данных включает блок предвыборки команд и внутреннюю кэш-память процессора (кэш первого уровня).

Блок предвыборки команд осуществляет формирование очереди команд, причем выборка из памяти осуществляется в промежутках между магистральными циклами команд.

Во внутренней кэш-памяти осуществляется буферизация часто используемых команд и данных. Благодаря этому существенно повышается производительность процессора, сокращается число обращений к ОП.

Устройство управления памятью (диспетчер памяти) предназначено для сопряжения ЦП и подсистемы ввода/вывода с ОП. Оно состоит из блока сегментации и блока страничной адресации, осуществляющих двухступенчатое формирование физического адреса ячейки памяти: сначала в пределах сегмента, а затем в пределах страницы.

Наличие двух этих блоков, их параллельное функционирование обеспечивают максимальную гибкость проектируемой системы.

Сегментация полезна для организации памяти локальных модулей и является инструментом программиста, в то время как страницы позволяют системному программисту эффективно использовать физическую память ЭВМ.

Интерфейс магистрали реализует протоколы обмена (связь по определенным правилам) ЦП с памятью, каналами (контроллерами) ввода/вывода и другими активными устройствами системы ЭВМ. Обмен осуществляется с помощью шин данных, адреса и управления.

В современных суперскалярных процессорах может использоваться от 2 до 6 параллельно работающих исполнительных устройств. Это могут быть:

- несколько целочисленных устройств;

- устройство плавающей точки (блок FPU);

- устройство выполнения переходов;

- устройство загрузки/записи.

Устройство выполнения переходов обрабатывает команды условных переходов. Если условия перехода доступны, то решение о направлении перехода принимается немедленно, в противном случае выполнение последующих команд продолжается по предположению (спекулятивно).

Пересылки данных между кэш-памятью данных, с одной стороны, и регистрами общего назначения и регистрами плавающей точки, с другой, обрабатываются устройством загрузки/записи.

Говоря о внутренней архитектуре процессора, не следует забывать и о его характеристиках, главная из которых – производительность, то есть число итераций, выполняемых за одну секунду. Производительность, в свою очередь, характеризуется радом параметров:

- степенью интеграции;

- внутренней и внешней разрядностью обработки данных;

- тактовой частотой;

- памятью, к которой может адресоваться процессор;

- объемом и устройством кэш-памяти.

Степень интеграции процессора

Внутренняя разрядность данных – количество бит, которое процессор может обрабатывать одновременно. Особенно важна эта характеристика для арифметических команд, выполняемых внутри ЦП.

Внешняя разрядность данных – разрядность системной шины. Тактовая частота современных процессоров превышает 300 МГц, тактовая частота системной шины составляет лишь 66 МГц. В самых последних моделях материнских плат – порядка 100 и 133 МГц, поэтому разрядность системной шины важна для эффективной работы ЦП.

Тактовая частота – количество циклов (или машинных тактов) в секунду, вырабатываемых генератором тактовых сигналов. Современные персональные компьютеры имеют несколько тактовых генераторов, работающих синхронно на различных частотах. Говоря о тактовой частоте системы, имеют в виду тактовую частоту системной шины.

Ширина ША, или количество ячеек памяти, к которым может адресоваться процессор.

Ширина ШД, или количество бит данных, которые могут быть одновременно переданы по ШД.

3. Регистровые структуры центрального процессора

Набор регистров и их структуры рассмотрим на примере процессоров IntelсCISC-архитектурой. Можно выделить следующие группы регистров:

- Основные функциональные регистры (используются при выполнении прикладных программ):регистры общего назначения (РОН);

- указатель команд;

- регистр флагов;

- регистры сегментов.

- Регистры процессора (FPU) обработки чисел с плавающей точкой (используются при выполнении прикладных программ):

- регистры данных;

- регистр тегов;

- регистр состояния;

- регистр указателей команд и данных FPU;

- регистр управления FPU.

- Системные регистры (используются при выполнении системных программ):

- регистры управления микропроцессора;

- регистры системных адресов.

- Регистры отладки и тестирования (используются при отладке и тестировании). Все 16-разрядные регистры микропроцессоров 8086, 80186, 80286 входят в состав набора 32-разрядных регистров.

Память.

Рядом с процессором, в специальном слоте находится модуль оперативной памяти или оперативное запоминающее устройство. Это набор микросхем, предназначенных для временного хранения данных, при включенном компьютере. В ОЗУ хранятся выполняемые программы и данные, которые они обрабатывают (Например, если мы работаем в Microsoft Office Word в ОЗУ находится данная программа и текст, с которым мы работаем. Если документ не сохранить, т.е. не записать во внешнюю память (винчестер, флэшка), то при выключении компьютера данные будут потеряны). При выборе оперативной памяти нужно обратить внимание на тип памяти, ее объем и частоту.

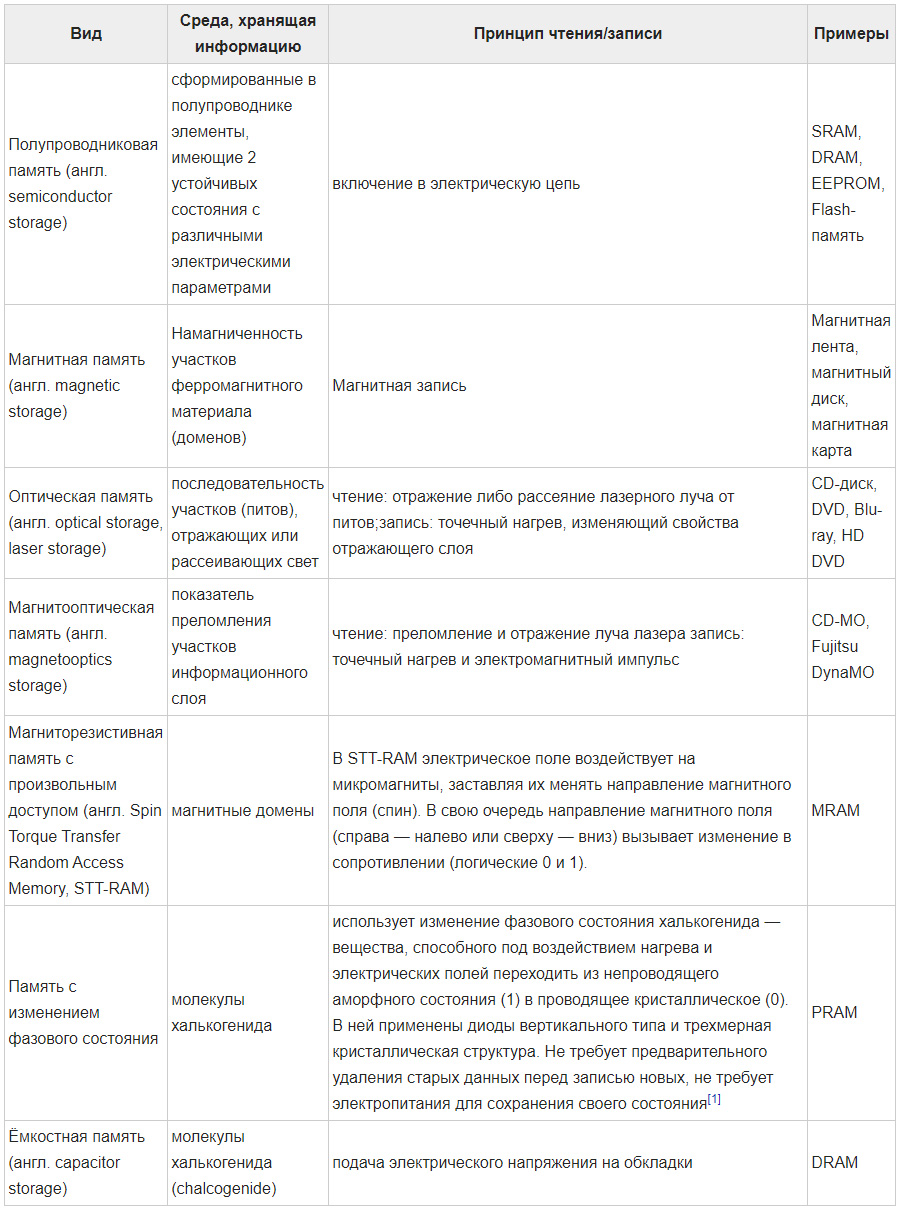

Следует различать классификацию памяти и классификацию запоминающих устройств (ЗУ). Первая классифицирует память по функциональности, вторая же — по технической реализации. Здесь рассматривается первая — таким образом, в неё попадают как аппаратные виды памяти (реализуемые на ЗУ), так и структуры данных, реализуемые в большинстве случаев программно.

Доступные операции над данными в памяти

- Память только для чтения (read-only memory, ROM).

- Память для чтения/записи.Память на программируемых и перепрограммируемых ПЗУ (ППЗУ и ПППЗУ) не имеет общепринятого места в этой классификации. Её относят либо к подвиду памяти «только для чтения», либо выделяют в отдельный вид.

Также предлагается относить память к тому или иному виду по характерной частоте её перезаписи на практике: к RAM относить виды, в которых информация часто меняется в процессе работы, а к ROM — предназначенные для хранения относительно неизменных данных.

Энергозависимость.

- Энергонезависимая память (англ. nonvolatile storage) — память, реализованная ЗУ, записи в которых не стираются при снятии электропитания. К этому типу памяти относятся все виды памяти на ПЗУ и ППЗУ.

- Энергозависимая память (англ. volatile storage) — память, реализованная ЗУ, записи в которых стираются при снятии электропитания. К этому типу памяти относятся память на ОЗУ, кэш- память:

- Статическая память (англ. static storage) — энергозависимая память, которой для хранения информации достаточно сохранения питающего напряжения.

- Динамическая память (англ. dynamic storage) — энергозависимая памяти, в которой информация со временем разрушается (деградирует), и, кроме подачи электропитания, необходимо производить её периодическое восстановление (регенерацию).

Метод доступа.

- Последовательный доступ (англ. sequential access memory, SAM) — ячейки памяти выбираются (считываются) последовательно, одна за другой, в очерёдности их расположения. Вариант такой памяти — стековая память.

- Произвольный доступ (англ. random access memory, RAM) — вычислительное устройство может обратиться к произвольной ячейке памяти по любому адресу.

Назначение.

- Буферная память (англ. buffer storage) — память, предназначенная для временного хранения данных при обмене ими между различными устройствами или программами.

- Временная (промежуточная) память (англ. temporary (intermediate) storage) — память для хранения промежуточных результатов обработки.

- Кеш-память (англ. cache memory) — часть архитектуры устройства или программного обеспечения, осуществляющая хранение часто используемых данных для предоставления их в более быстрый доступ, нежели кешируемая память.

- Корректирующая память (англ. patch memory) — часть памяти ЭВМ, предназначенная для хранения адресов неисправных ячеек основной памяти. Также используются термины «relocation table» и «remap table».

- Управляющая память (англ. control storage) — память, содержащая управляющие программы или микропрограммы. Обычно реализуется в виде ПЗУ.

- Разделяемая память или память коллективного доступа (англ. shared memory, shared access memory) — память, доступная одновременно нескольким пользователям, процессам или процессорам.

Организация адресного пространства.

- Реальная или физическая память (англ. real (physical) memory) — память, способ адресации которой соответствует физическому расположению её данных.

- Виртуальная память (англ. virtual memory) — память, способ адресации которой не отражает физического расположения её данных.

- Оверлейная память (англ. overlayable storage) — память, в которой присутствует несколько областей с одинаковыми адресами, из которых в каждый момент доступна только одна.

Удалённость и доступность для процессора.

- Первичная память доступна процессору без какого-либо обращения к внешним устройствам. Это регистры процессора (процессорная или регистровая память) и кэш процессора (если есть).

- Вторичная память доступна процессору путём прямой адресацией через шину адреса (Адресуемая память) или через другие выводы. Таким образом доступна основная память (память, предназначенная для хранения текущих данных и выполняемых программ) и порты ввода-вывода (специальные адреса, через обращение к которым реализовано взаимодействие с прочей аппаратурой).

- Третичная память доступна только путём нетривиальной последовательности действий. Сюда входят все виды внешней памяти — доступной через устройства ввода-вывода. Взаимодействие с третичной памятью ведётся по определённым правилам (протоколам) и требует присутствия в памяти соответствующих программ. Программы, обеспечивающие минимально необходимое взаимодействие, помещаются в ПЗУ, входящее во вторичную память (у PC-совместимых ПК — это ПЗУ BIOS).

Положение структур данных, расположенных в основной памяти, в этой классификации неоднозначно. Как правило, их вообще в неё не включают, выполняя классификацию с привязкой к традиционно используемым видам ЗУ.

Управление процессором.

- Непосредственно управляемая (оперативно доступная) память (англ. on-line storage) — память, непосредственно доступная в данный момент времени центральному процессору.

- Автономная память.

Организация хранения данных и алгоритмы доступа к ним.

-

- Повторяет классификацию структур данных.

- Адресуемая память — адресация осуществляется по местоположению данных.

- Ассоциативная память (англ. associative memory, content- addressable memory, CAM) — адресация осуществляется по содержанию данных, а не по их местоположению.

- Магазинная (стековая) память (англ. pushdown storage) — реализация стека.

- Матричная память (англ. matrix storage) — ячейки памяти расположены так, что доступ к ним осуществляется по двум или более координатам.

- Объектная память (англ. object storage) — память, система управления которой ориентирована на хранение объектов. При этом каждый объект характеризуется типом и размером записи.

- Семантическая память (англ. semantic storage) — данные размещаются и списываются в Физические принципы.

Эта классификация повторяет соответствующую классификацию ЗУ.

Разновидности магнитной памяти.

- Память на магнитной ленте (англ. magnetic tape memory) — представляет собой пластиковую узкую ленту с магнитным покрытием и механизм с блоком головок записи-воспроизведения (БГЗВ). Лента намотана на бобину, и последовательно протягивается лентопротяжным механизмом (ЛПМ) возле БГЗВ. Запись производится перемагничиванием частиц магнитного слоя ленты при прохождении их возле зазора головки записи. Считывание записанной информации происходит при прохождении намагниченного ранее участка плёнки возле зазора головки воспроизведения.

- Память на магнитных дисках (англ. magnetic disk memory) — представляет собой круглый пластиковый диск с магнитным покрытием и механизм с БГЗВ. Данные при этом наносятся радиально, при вращении диска вокруг своей оси и радиальном сдвиге БГЗВ на шаг головки. Запись производится перемагничиванием частиц магнитного слоя диска при прохождении их возле зазора головки записи. Считывание записанной информации происходит при прохождении намагниченного ранее участка возле зазора головки воспроизведения.

- Память на магнитной проволоке (англ. plated wire memory) Использовалась в магнитофонах до магнитной ленты. В настоящее время по этому принципу конструируется большинство авиационных т.н. «чёрных ящиков» — данный носитель имеет наиболее высокую устойчивость к внешним воздействиям и высокую сохранность даже при повреждениях в аварийных ситуациях.

- Ферритовая память (англ. core storage) — ячейка представляет собой ферритовый сердечник, изменение состояния которого (перемагничивание) происходит при пропускании тока через намотанный на него проводник. В настоящее имеет ограниченное применение, в основном в военной сфере.

Разновидности оптической памяти.

- Фазоинверсная память (англ. Phase Change Rewritable storage, PCR) — оптическая память, в которой рабочий (отражающий) слой выполнен из полимерного вещества, способного при нагреве менять фазовое состояние (кристаллическое↔аморфное) и отражающие характеристики в зависимости от режима нагрева. Применяется в перезаписываемых оптических дисках (CD-RW, DVD-RW).

Память ROM, SRAM, DRAM.

В современных компьютерах используются запоминающие устройства трех основных типов:

- ROM (Read Only Memory). Постоянное запоминающее устройство — ПЗУ, неспособное выполнять операцию записи данных.

- DRAM (Dynamic Random Access Memory). Динамическое запоминающее устройство с произвольным порядком выборки.

- SRAM (Static RAM). Статическая оперативная память.

Память типа ROM.

В памяти типа ROM (Read Only Memory), или ПЗУ (постоянное запоминающее устройство), данные можно только хранить, изменять их нельзя. Именно поэтому такая память используется только для чтения данных. ROM также часто называется энергонезависимой памятью, потому что любые данные, записанные в нее, сохраняются при выключении питания. Поэтому в ROM помещаются команды запуска ПК, т.е. программное обеспечение, которое загружает систему.

Рис. 3. ROM-память

ROM и оперативная память — не противоположные понятия. На самом деле ROM представляет собой часть оперативной памяти системы. Другими словами, часть адресного пространства оперативной памяти отводится для ROM. Это необходимо для хранения программного обеспечения, которое позволяет загрузить операционную систему.

Основной код BIOS содержится в микросхеме ROM на системной плате, но на платах адаптеров также имеются аналогичные микросхемы. Они содержат вспомогательные подпрограммы BIOS и драйверы, необходимые для конкретной платы, особенно для тех плат, которые должны быть активизированы на раннем этапе начальной загрузки, например видеоадаптер. Платы, не нуждающиеся в драйверах на раннем этапе начальной загрузки, обычно не имеют ROM, потому что их драйверы могут быть загружены с жесткого диска позже — в процессе начальной загрузки.

Рис. 4. ROM-память

В настоящее время в большинстве систем используется одна из форм Flash-памяти, которая называется электрически стираемой программируемой постоянной памятью (Electrically Erasable Programmable Readonly Memory — EEPROM). Flash-память является по- настоящему энергонезависимой и перезаписываемой, она позволяет пользователям легко модифицировать ROM, программно-аппаратные средства системных плат и других компонентов (таких, как видеоадаптеры, платы SCSI, периферийные устройства и т.п.).

SRAM(кэш-память).

Существует тип памяти, совершенно отличный от других, — статическая оперативная память (Static RAM — SRAM). Она названа так потому, что, в отличие от динамической оперативной памяти (DRAM), для сохранения ее содержимого не требуется периодической регенерации. Это не единственное ее преимущество. SRAM имеет более высокое быстродействие, чем DRAM, и может работать на той же частоте, что и современные процессоры.

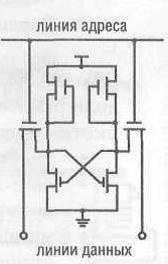

Статическая память — это тип памяти, в котором значение бита информация хранится в ячейке определяющаяся наличием или отсутствием заряда на миниатюрном конденсаторе (управляемом транзисторами).

В статической памяти применяются специальные элементы — триггеры, реализованные на 4-6 транзисторах. Именно триггер является ячейкой статической памяти.

Рис. 5. Схема ячейки статической памяти

Транзистор – трехэлектродный полупроводниковый прибор для усиления, генерирования и преобразования электрических колебаний, выполненный на основе монокристаллического полупроводника.

Триггер — логический элемент с двумя устойчивыми состояниями равновесия, предназначенное для записи и хранения информации. Такое устройство сохраняет свое состояние, до тех пор, пока подается питание. Время срабатывания триггера составляет в современных микросхемах не более 2нс (Pentium 4 3,6 GHz = 0.28нс; Athlon XP 2,2GHz = 0.41нс). SRAM различается по принципу работы.

Существует три типа:

- Async SRAM (Asynchronous Static Random Access Memory) — асинхронная статическая память с произвольным порядком выборки.

- SyncBurst SRAM (Synchronous Burst Random Access Memory) – синхронная пакетная статическая память с произвольным порядком выборки.

- PipBurst SRAM (Pipelined Burst Random Access Memory) – конвейерная пакетная статическая память с произвольным порядком выборки.

Async SRAM – это устаревший тип памяти, асинхронный интерфейс которой схож с интерфейсом DRAM и включает в себя шины адреса, данных и управления.

SyncBurst SRAM – этот тип памяти синхронизирован с системной шиной и лучше всего подходит для выполнения пакетных операций. Ну а интерфейс PipBurst SRAM схож с интерфейсом SyncBurst SRAM, но позволяет получать данные без тактов ожидания.

Как правило, чем больше объем кэш, тем система производительней. Но сам по себе объем еще не гарантирует высокой производительности. Для кэш главное – контроллер.

Время доступа SRAM 2 нс. означает, что такая память может работать синхронно с процессорами на частоте 500 МГц или выше. Однако для хранения каждого бита в конструкции SRAM используется кластер из шести транзисторов. Использование транзисторов без каких либо конденсаторов означает, что нет необходимости в регенерации. (Ведь если нет никаких конденсаторов, то и заряды не теряются.) Пока подается питание, SRAM будет помнить то, что сохранено.

По сравнению с DRAM быстродействие SRAM намного выше, но плотность ее гораздо ниже, а цена довольно высока. Более низкая плотность означает, что микросхемы SRAM имеют большие габариты, хотя их информационная емкость намного меньше. Большое число транзисторов и кластеризованное их размещение не только увеличивает габариты микросхем SRAM, но и значительно повышает стоимость технологического процесса по сравнению с аналогичными параметрами для микросхем DRAM. Например, емкость модуля DRAM может равняться 64 Мбайт или больше, в то время как емкость модуля SRAM приблизительно того же размера составляет только 2 Мбайт, причем их стоимость будет одинаковой. Таким образом, габариты SRAM в среднем в 30 раз превышают размер DRAM, то же самое можно сказать и о стоимости. Все это не позволяет использовать память типа SRAM в качестве оперативной памяти в персональных компьютерах.

Память типа DRAM.

DRAM (Dynamic Random Access Memory) — тип энергозависимой полупроводниковой памяти с произвольным доступом (RAM), также запоминающее устройство, наиболее широко используемое в качестве ОЗУ современных компьютеров.

Физически память DRAM состоит из ячеек, созданных в полупроводниковом материале, в каждой из которых можно хранить определённый объём данных, от 1 до 4 бит. Совокупность ячеек такой памяти образуют условный «прямоугольник», состоящий из определённого количества строк и столбцов. Один такой «прямоугольник» называется страницей, а совокупность страниц называется банком. Весь набор ячеек условно делится на несколько областей.

Рис. 6. Схема ячейки динамической памяти

Основное преимущество памяти этого типа состоит в том, что ее ячейки упакованы очень плотно, т.е. в небольшую микросхему можно упаковать много битов, а значит, на их основе можно построить память большой емкости.

Ячейки памяти в микросхеме DRAM — это крошечные конденсаторы, которые удерживают заряды. Именно так (наличием или отсутствием зарядов) и кодируются биты. Проблемы, связанные с памятью этого типа, вызваны тем, что она динамическая, т.е. должна постоянно регенерироваться, так как в противном случае электрические заряды в конденсаторах памяти будут «стекать» и данные будут потеряны. Регенерация происходит, когда контроллер памяти системы берет крошечный перерыв и обращается ко всем строкам данных в микросхемах памяти. Большинство систем имеют контроллер памяти (обычно встраиваемый в набор микросхем системной платы), который настроен на соответствующую промышленным стандартам частоту регенерации, равную, например, 15 мкс.

Ко всем строкам данных обращение осуществляется по прохождении 128 специальных циклов регенерации. Это означает, что каждые 1,92 мс (128×15 мкс) прочитываются все строки в памяти для обеспечения регенерации данных.

Регенерация памяти, к сожалению, отнимает время у процессора: каждый цикл регенерации по длительности занимает несколько циклов центрального процессора. В старых компьютерах циклы регенерации могли занимать до 10% (или больше) процессорного времени, но в современных системах, работающих на частотах, равных сотням мегагерц, расходы на регенерацию составляют 1% (или меньше) процессорного времени. Некоторые системы позволяют изменить параметры регенерации с помощью программы установки параметров CMOS, но увеличение времени между циклами регенерации может привести к тому, что в некоторых ячейках памяти заряд “стечет”, а это вызовет сбои памяти. В большинстве случаев надежнее придерживаться рекомендуемой или заданной по умолчанию частоты регенерации. Поскольку затраты на регенерацию в современных компьютерах составляют менее 1%, изменение частоты регенерации оказывает незначительное влияние на характеристики компьютера. Одним из наиболее приемлемых вариантов является использование для синхронизации памяти значений по умолчанию или автоматических настроек, заданных с помощью Setup BIOS. Большинство современных систем не позволяют изменять заданную синхронизацию памяти, постоянно используя автоматически установленные параметры. При автоматической установке системная плата считывает параметры синхронизации из системы определения последовательности в ПЗУ (serial presence detect — SPD) и устанавливает частоту периодической подачи импульсов в соответствии с полученными данными.

В устройствах DRAM для хранения одного бита используется только один транзистор и пара конденсаторов, поэтому они более вместительны, чем микросхемы других типов памяти. В настоящее время имеются микросхемы динамической оперативной памяти емкостью 4 Гбайт и больше. Это означает, что подобные микросхемы содержат более миллиарда транзисторов. В микросхеме памяти все транзисторы и конденсаторы размещаются последователь но, обычно в узлах квадратной решетки, в виде очень простых, периодически повторяющихся структур.

Транзистор для каждого одноразрядного регистра DRAM используется для чтения состояния смежного конденсатора. Если конденсатор заряжен, в ячейке записана 1; если заряда нет — записан 0. Заряды в крошечных конденсаторах все время стекают, вот почему память должна постоянно регенерироваться. Даже мгновенное прерывание подачи питания или какой-нибудь сбой в циклах регенерации приведет к потере заряда в ячейке DRAM, а следовательно, и к потере данных. В работающей системе подобное приводит к появлению “синего” экрана, глобальным отказам системы защиты, повреждению файлов или к полному отказу системы.

Динамическая оперативная память используется в персональных компьютерах; поскольку она недорогая, микросхемы могут быть плотно упакованы, а это означает, что запоминающее устройство большой емкости может занимать небольшое пространство. К сожалению, память этого типа не отличается высоким быстродействием, обычно она намного “медленнее” процессора. Поэтому существует множество различных типов организации DRAM, позволяющих улучшить эту характеристику.

Характеристики памяти DRAM.

Основными характеристиками DRAM являются рабочая частота и тайминги.

При обращении к ячейке памяти контроллер памяти задаёт номер банка, номер страницы в нём, номер строки и номер столбца и на все эти запросы тратится время, помимо этого довольно большой период уходит на открытие и закрытие банка после самой операции. На каждое действие требуется время, называемое таймингом.

Основными таймингами DRAM являются:

- задержка между подачей номера строки и номера столбца, называемая временем полного доступа (англ. RAS to CAS delay);

- задержка между подачей номера столбца и получением содержимого ячейки, называемая временем рабочего цикла (англ. CAS delay);

- задержка между чтением последней ячейки и подачей номера новой строки (англ. RAS precharge).

Тайминги измеряются в наносекундах, и чем меньше величина этих таймингов, тем быстрее работает оперативная память.

Типы DRAM.

На протяжении долгого времени разработчиками создавались различные типы памяти. Они обладали разными характеристиками, в них были использованы разные технические решения. Основной движущей силой развития памяти было развитие компьютеров и центральных процессоров. Постоянно требовалось увеличение быстродействия и объёма оперативной памяти.

- Страничная память.

Страничная память (англ. page mode DRAM, PM DRAM) являлась одним из первых типов выпускаемой компьютерной оперативной памяти. Память такого типа выпускалась в начале 1990-х годов, но с ростом производительности процессоров и ресурсоёмкости приложений требовалось увеличивать не только объём памяти, но и скорость её работы.

-

- Быстрая страничная память.

Быстрая страничная память (англ. fast page mode DRAM, FPM DRAM) появилась в 1995 году. Принципиально новых изменений память не претерпела, а увеличение скорости работы достигалось путём повышенной нагрузки на аппаратную часть памяти. Данный тип памяти в основном применялся для компьютеров с процессорами Intel 80486 или аналогичных процессоров других фирм. Память могла работать на частотах 25 и 33 МГц с временем полного доступа 70 и 60 нс и с временем рабочего цикла 40 и 35 нс соответственно.

Модули оперативной памяти SDRAM, DDR SDRAM, DDR2 SDRAM, DDR3 SDRAM, DDR4 SDRAM и др.

EDO DRAM — память с усовершенствованным выходом.

C появлением процессоров Intel Pentium память FPM DRAM оказалась совершенно неэффективной. Поэтому следующим шагом стала память с усовершенствованным выходом (англ. extended data out DRAM, EDO DRAM). Эта память появилась на рынке в 1996 году и стала активно использоваться на компьютерах с процессорами Intel Pentium и выше. Её производительность оказалась на 10—15 % выше по сравнению с памятью типа FPM DRAM. Её рабочая частота была 40 и 50 МГц, соответственно, время полного доступа — 60 и 50 нс, а время рабочего цикла — 25 и 20 нс. Эта память содержит регистр-защелку (англ. data latch) выходных данных, что обеспечивает некоторую конвейеризацию работы для повышения производительности при чтении.

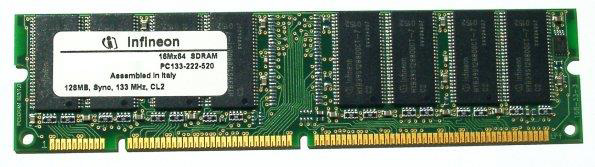

SDRAM — синхронная DRAM.

В связи с выпуском новых процессоров и постепенным увеличением частоты системной шины, стабильность работы памяти типа EDO DRAM стала заметно падать. Ей на смену пришла синхронная память (англ. synchronous DRAM, SDRAM). Новыми особенностями этого типа памяти являлись использование тактового генератора для синхронизации всех сигналов и использование конвейерной обработки информации. Также память надёжно работала на более высоких частотах системной шины (100 МГц и выше).

Report this ad.

Рис. 7. Модуль памяти SD RAM

Если для FPM и EDO памяти указывается время чтения первой ячейки в цепочке (время доступа), то для SDRAM указывается время считывания последующих ячеек. Цепочка — несколько последовательных ячеек. На считывание первой ячейки уходит довольно много времени (60-70 нс) независимо от типа памяти, а вот время чтения последующих сильно зависит от типа. Рабочие частоты этого типа памяти могли равняться 66, 100 или 133 МГц, время полного доступа — 40 и 30 нс, а время рабочего цикла — 10 и 7,5 нс.

С этим типом памяти применялась технология Virtual Channel Memory (VCM). VCM использует архитектуру виртуального канала, позволяющую более гибко и эффективно передавать данные с использованием каналов регистра на чипе. Данная архитектура интегрирована в SDRAM. VCM, помимо высокой скорости передачи данных, была совместима с существующими SDRAM, что позволяло делать апгрейд системы без значительных затрат и модификаций. Это решение нашло поддержку у некоторых производителей чипсетов.

Enhanced SDRAM (ESDRAM).

Для преодоления некоторых проблем с задержкой сигнала, присущих стандартной DRAM-памяти, было решено встроить небольшое количество SRAM в чип, то есть создать на чипе кеш— это, по существу, SDRAM с небольшим количеством SRAM. При малой задержке и пакетной работе достигается частота до 200 МГц. Как и в случае внешней кеш-памяти, SRAM-кеш предназначен для хранения и выборки наиболее часто используемых данных. Отсюда и уменьшение времени доступа к данным медленной DRAM.

Одним из таких решений являлась ESDRAM от Ramtron International Corporation.

Рис. 8. Модули ESDRAM

Пакетная EDO RAM.

Пакетная память EDO RAM (англ. burst extended data output DRAM, BEDO DRAM) стала дешёвой альтернативой памяти типа SDRAM. Основанная на памяти EDO DRAM, её ключевой особенностью являлась технология поблочного чтения данных (блок данных читался за один такт), что сделало её работу быстрее, чем у памяти типа SDRAM. Однако невозможность работать на частоте системной шины более 66 МГц не позволила данному типу памяти стать популярным.

Рис. 9. Модуль EDORAM

Video RAM.

Специальный тип оперативной памяти — Video RAM (VRAM) — был разработан на основе памяти типа SDRAM для использования в видеоплатах. Он позволял обеспечить непрерывный поток данных в процессе обновления изображения, что было необходимо для реализации изображений высокого качества. На основе памяти типа VRAM, появилась спецификация памяти типа Windows RAM (WRAM), иногда её ошибочно связывают с операционными системами семейства Windows. Её производительность стала на 25 % выше, чем у оригинальной памяти типа SDRAM, благодаря некоторым техническим изменениям.

Рис. 10. Микросхема Video RAM

DDR SDRAM.

По сравнению с обычной памятью типа SDRAM, в памяти SDRAM с удвоенной скоростью передачи данных (англ. double data rate SDRAM, DDR SDRAM или SDRAM II) была вдвое увеличена пропускная способность. Первоначально память такого типа применялась в видеоплатах, но позднее появилась поддержка DDR SDRAM со стороны чипсетов.

У всех предыдущих DRAM были разделены линии адреса, данных и управления, которые накладывают ограничения на скорость работы устройств. Для преодоления этого ограничения в некоторых технологических решениях все сигналы стали выполняться на одной шине. Двумя из таких решений являются технологии DRDRAM и SLDRAM. Они получили наибольшую популярность и заслуживают внимания. Стандарт SLDRAM является открытым и, подобно предыдущей технологии, SLDRAM использует оба перепада тактового сигнала. Что касается интерфейса, то SLDRAM перенимает протокол, названный SynchLink Interface и стремится работать на частоте 400 МГц.

Рис. 11. Модуль DDR SDRAM

Память DDR SDRAM работает на частотах в 100, 133, 166 и 200 МГц, её время полного доступа — 30 и 22,5 нс, а время рабочего цикла — 5, 3,75, 3 и 2,5 нс.

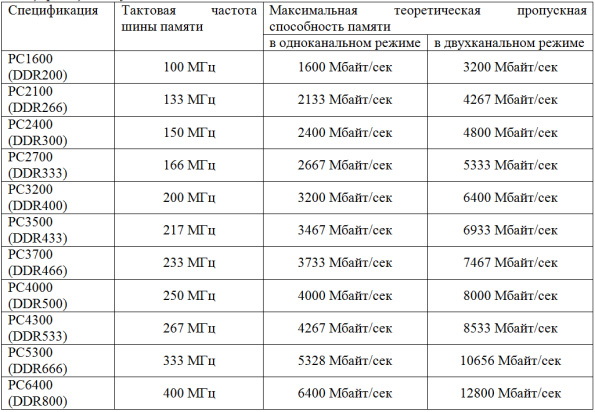

Так как частота синхронизации лежит в пределах от 100 до 200 МГц, а данные передаются по 2 бита на один синхроимпульс, как по фронту, так и по срезу тактового импульса, то эффективная частота передачи данных лежит в пределах от 200 до 400 МГц. Такие модули памяти обозначаются DDR200, DDR266, DDR333, DDR400.

Direct RDRAM или Direct Rambus DRAM.

Тип памяти RDRAM является разработкой компании Rambus. Высокое быстродействие этой памяти достигается рядом особенностей, не встречающихся в других типах памяти. Первоначальная очень высокая стоимость памяти RDRAM привела к тому, что производители мощных компьютеров предпочли менее производительную, зато более дешёвую память DDR SDRAM. Рабочие частоты памяти — 400, 600 и 800 МГц, время полного доступа — до 30 нс, время рабочего цикла — до 2,5 нс.

Рис. 12. Модули RD RAM

DDR2 SDRAM.

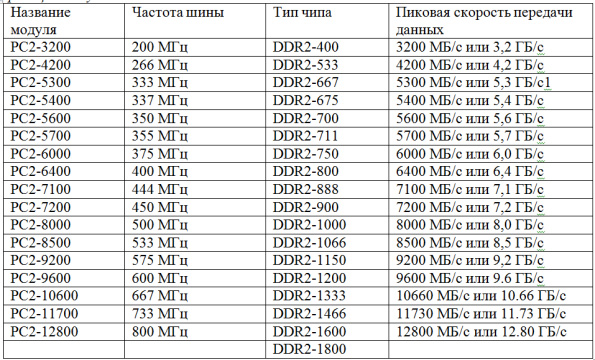

Конструктивно новый тип оперативной памяти DDR2 SDRAM был выпущен в 2004 году. Основываясь на технологии DDR SDRAM, этот тип памяти за счёт технических изменений показывает более высокое быстродействие и предназначен для использования на современных компьютерах. Память может работать с тактовой частотой шины 200, 266, 333, 337, 400, 533, 575 и 600 МГц. При этом эффективная частота передачи данных соответственно будет 400, 533, 667, 675, 800, 1066, 1150 и 1200 МГц. Некоторые производители модулей памяти помимо стандартных частот выпускают и образцы, работающие на нестандартных (промежуточных) частотах. Они предназначены для использования в разогнанных системах, где требуется запас по частоте. Время полного доступа — 25, 11,25, 9, 7,5 нс и менее. Время рабочего цикла — от 5 до 1,67 нс.

Рис. 13. Модуль DDR2 SDRAM

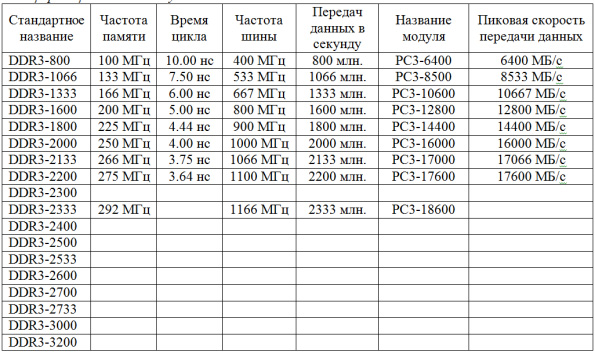

DDR3 SDRAM.

Этот тип памяти основан на технологиях DDR2 SDRAM со вдвое увеличенной частотой передачи данных по шине памяти. Отличается пониженным энергопотреблением по сравнению с предшественниками. Частота полосы пропускания лежит в пределах от 800 до 2400 МГц (рекорд частоты — более 3000 МГц), что обеспечивает большую пропускную способность по сравнению со всеми предшественниками.

Рис. 14. Модуль DDR3 SDRAM

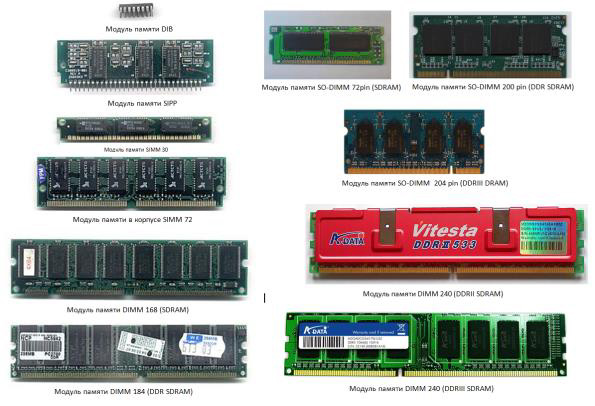

Конструктивные исполнения памяти DRAM.

Память типа DRAM конструктивно выполняют и в виде отдельных микросхем в корпусах типа DIP, SOIC, BGA, и в виде модулей памяти типа: SIPP, SIMM, DIMM, RIMM.

Первоначально микросхемы памяти выпускались в корпусах типа DIP (к примеру, серия К565РУхх), далее они стали производится в более технологичных для применения в модулях корпусах.

На многих модулях SIMM и подавляющем числе DIMM устанавливалась SPD (Serial Presence Detect) — небольшая микросхема памяти EEPROM, хранящая параметры модуля (ёмкость, тип, рабочее напряжение, число банков, время доступа и т. п.), которые программно были доступны как оборудованию, в котором модуль был установлен (применялось для автонастройки параметров), так и пользователям и производителям.

Модули SIPP.

Модули типа SIPP (Single In-line Pin Package) представляют собой прямоугольные платы с контактами в виде ряда маленьких штырьков. Этот тип конструктивного исполнения уже практически не используется, так как он далее был вытеснен модулями типа SIMM.

Модули SIMM.

Модули типа SIMM (Single In-line Memory Module) представляют собой длинные прямоугольные платы с рядом контактных площадок вдоль одной из её сторон. Модули фиксируются в разъёме (сокете) подключения с помощью защёлок, путём установки платы под некоторым углом и нажатия на неё до приведения в вертикальное положение. Имели несколько модификаций, среди которых наибольшее распространение получили три.

Первая — 30-контактный модуль, имевший объем от 256 КБайт до 16 МБайт и восьмиразрядную шину данных, дополняемую (иногда) девятой линией контроля четности памяти. Применялся в 286, 386 машинах. В случае процессоров 286, 386SX модули ставились парами, на 386DX — по четыре штуки одинаковой емкости.

30-контактный модуль SIMM.

С приходом 486 машин, для которых эти модули надо было бы ставить по четыре (как минимум) штуки был вытеснен 72-контактным модулем SIMM, который, по существу, объединил на себе 4 30- контактных модуля с общими линиями адреса и раздельными линиями данных. Таким образом, модуль становится 32-разрядным и достаточно всего одного модуля. Объем от 1 МБайт до 128 МБайт.

Характеристики:

- Разрядность шины данных: 8 бит (9 бит у модулей с контролем четности).

- Тип применяемых микросхем динамической памяти: FPM.

- Стандартные значения объема памяти модулей: 256 Кб, 1 Мб, 4 Мб, 16 Мб.

- Шаг расположения контактных площадок — 0,1’’.

Таким образом модули выпускались на 4, 8, 16, 32, 64, 128 Мбайт. Наиболее распространены 30- и 72-контактные модули SIMM.

Модули DIMM.

Модули типа DIMM (Dual In-line Memory Module) представляют собой длинные прямоугольные платы с рядами контактных площадок вдоль обеих её сторон, устанавливаемые в разъём подключения вертикально и фиксируемые по обоим торцам защёлками. Микросхемы памяти на них могут быть размещены как с одной, так и с обеих сторон платы. DIMM (англ. Dual In-line Memory Module, двухсторонний модуль памяти) — форм-фактор модулей памяти DRAM. Данный форм-фактор пришёл на смену форм-фактору SIMM. Основным отличием DIMM от предшественника является то, что контакты, расположенные на разных сторонах модуля являются независимыми, в отличие от SIMM, где симметричные контакты, расположенные на разных сторонах модуля, замкнуты между собой и передают одни и те же сигналы. Кроме того, DIMM имеет 64 (без контроля чётности) или 72 (с контролем по чётности или коду ECC) линии передачи данных, в отличие от SIMM c 32 линиями.

Конструктивно представляет собой длинную прямоугольную плату с рядами контактных площадок вдоль обеих её сторон, устанавливаемую в разъём подключения вертикально и фиксируемый по обоим её торцам защёлками. Микросхемы памяти могут быть размещены как с одной, так и с обеих сторон платы.

В отличие от форм-фактора SIMM, используемого для асинхронной памяти FPM и EDO, форм-фактор DIMM предназначен для памяти типа SDRAM. Изготавливались модули рассчитанные на напряжение питания 3,3 В и (реже) 5 В.

В дальнейшем, в модули DIMM стали упаковывать память типа DDR, DDR II и DDR III, отличающуюся повышенным быстродействием.

Появлению форм-фактора DIMM способствовало появление процессора Pentium, который имел 64-разрядную шину данных. В профессиональных рабочих станциях, таких, как SPARCstation, такой тип памяти использовался с начала 1990-х годов. В компьютерах общего назначения широкий переход на этот тип памяти произошёл в конце 1990- х, примерно во времена процессора Pentium II.

Существуют следующие типы DIMM:

- 72-pin SO-DIMM (не совместима с 72-pin SIMM) — используется для FPM DRAM и EDO DRAM.

- 100-pin DIMM — используется для принтеров SDRAM.

- 144-pin SO-DIMM — используется для SDR SDRAM.

- 168-pin DIMM — используется для SDR SDRAM (реже для FPM/EDO DRAM в рабочих станциях/серверах).

- 172-pin MicroDIMM — используется для DDR SDRAM.

- 184-pin DIMM — используется для DDR SDRAM.

- 200-pin SO-DIMM — используется для DDR SDRAM и DDR2 SDRAM.

- 214-pin MicroDIMM — используется для DDR2 SDRAM.

- 204-pin SO-DIMM — используется для DDR3 SDRAM.

- 240-pin DIMM — используется для DDR2 SDRAM, DDR3 SDRAM и FB-DIMM DRAM.

Модули памяти типа SDRAM наиболее распространены в виде 168- контактных DIMM-модулей, памяти типа DDR SDRAM — в виде 184- контактных, а модули типа DDR2, DDR3 и FB-DIMM SDRAM — 204- контактных модулей.

Модули RIMM.

Модули типа RIMM (Rambus In-line Memory Module) менее распространены, в них выпускается память типа RDRAM. Они представлены 168- и 184-контактными разновидностями, причём на материнской плате такие модули обязательно должны устанавливаться только в парах, в противном случае в пустые разъёмы устанавливаются специальные модули-заглушки (это связано с особенностями конструкции таких модулей). Также существуют 242-контактные PC1066 RDRAM модули RIMM 4200, не совместимые с 184-контактными разъёмами, и уменьшенная версия RIMM — SO-RIMM, которые применяются в портативных устройствах.

Рис. 15. Модули памяти в различных форм факторах

История использования и основные характеристики.

Массовый выпуск SDRAM начался в 1993 году. Первоначально этот тип памяти предлагался в качестве альтернативы для дорогой видеопамяти (VRAM), однако вскоре SDRAM завоевал популярность и стал применяться в качестве ОЗУ, постепенно вытесняя другие типы динамической памяти. Последовавшие затем технологии DDR позволили сделать SDRAM ещё эффективнее. За разработкой DDR SDRAM, последовал стандарт DDR2 SDRAM, а затем и DDR3 SDRAM.

SDR SDRAM.

Первый стандарт SDRAM с появлением последующих стандартов стал именоваться SDR (Single Data Rate — в отличие от Double Data Rate). За один такт принималась одна управляющая команда и передавалось одно слово данных. Типичными тактовыми частотами были 66, 100 и 133 МГц. Микросхемы SDRAM выпускались с шинами данных различной ширины (обычно 4, 8 или 16 бит), но как правило, эти микросхемы входили в состав 168-пинного модуля DIMM, который позволял прочитать или записать 64 бита (в варианте без контроля чётности) или 72 бита (с контролем чётности) за один такт.

Использование шины данных в SDRAM оказалось осложнено задержкой в 2 или 3 такта между подачей сигнала чтения и появлением данных на шине данных, тогда как во время записи никакой задержки быть не должно. Потребовалась разработка достаточно сложного контроллера, который не позволял бы использовать шину данных для записи и для чтения в один и тот же момент времени.

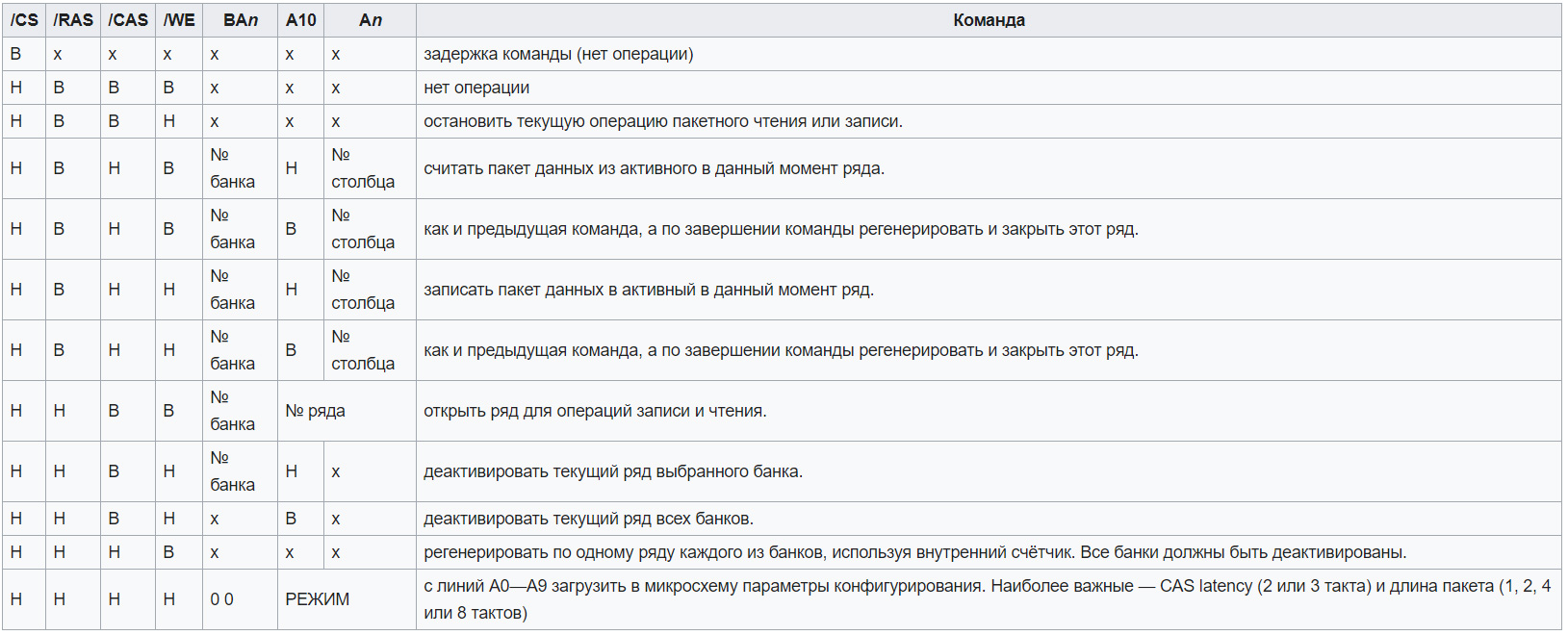

Управляющие сигналы.

Команды, управляющие модулем памяти SDR SDRAM, подаются на контакты модуля по 7 сигнальным линиям. По одной из них подается тактовый сигнал, передние(нарастающие) фронты которого задают моменты времени, в которые считываются команды управления с остальных 6 командных линий. Имена(в скобках — расшифровки имен) шести командных линий и описания команд приведены ниже:

- CKE (clock enable) — при низком уровне сигнала блокируется подача тактового сигнала на микросхему. Команды не обрабатываются, состояние других командных линий игнорируется.

- /CS (chip select) — при высоком уровне сигнала все прочие управляющие линии, кроме CKE, игнорируются. Действует как команда NOP (нет оператора).

- DQM (data mask) — высокий уровень на этой линии запрещает чтение/запись данных. При одновременно поданной команде записи данные не записываются в DRAM. Присутствие этого сигнала в двух тактах, предшествующих циклу чтения приводит к тому, что данные не считываются из памяти.

- /RAS (row address strobe) — несмотря на название, это не строб, а всего лишь один командный бит. Вместе с /CAS и /WE кодирует одну из 8 команд.

- /CAS (column address strobe) — несмотря на название, это не строб, а всего лишь один командный бит. Вместе с /RAS и /WE кодирует одну из 8 команд.

- /WE (write enable) — Вместе с /RAS и /CAS кодирует одну из 8 команд.

Устройства SDRAM внутренне разделены на 2 или 4 независимых банка памяти. Входы адреса первого и второго банка памяти (BA0 и BA1) определяют, какому банку предназначена текущая команда.

Принимаются следующие команды:

DDR SDRAM пришла на смену памяти типа SDRAM. При использовании DDR SDRAM достигается удвоенная скорость работы, нежели в SDRAM, за счёт считывания команд и данных не только по фронту, как в SDRAM, но и по спаду тактового сигнала. За счёт этого удваивается скорость передачи данных без увеличения частоты тактового сигнала шины памяти. Таким образом, при работе DDR на частоте 100 МГц мы получим эффективную частоту 200МГц (при сравнении с аналогом SDR SDRAM).

Описание.

Внешнее отличие — 184 контактов (по 92 с каждой стороны).

Микросхемы памяти DDR SDRAM выпускаются в корпусах TSOP и (освоено позднее) корпусах типа BGA (FBGA), производятся по нормам 0,13 и 0,09-микронного техпроцесса.

Напряжение питания микросхем: 2,6 В +/- 0,1 В. Потребляемая мощность: 527 мВт.

Интерфейс ввода-вывода: SSTL_2.

Ширина шины памяти составляет 64 бита, то есть по шине за один такт одновременно передаётся 8 байт. В результате получаем следующую формулу для расчёта максимальной скорости передачи для заданного типа памяти: тактовая частота шины памяти x 2 (передача данных дважды за такт) x 8 (число байтов передающихся за один такт). Например, чтобы обеспечить передачу данных дважды за такт, используется специальная архитектура «2n Prefetch». Внутренняя шина данных имеет ширину в два раза больше внешней. При передаче данных сначала передаётся первая половина шины данных по фронту тактового сигнала, а затем вторая половина шины данных по спаду.

Помимо удвоенной передачи данных, DDR SDRAM имеет несколько других принципиальных отличий от простой памяти SDRAM. В основном они являются технологическими. Например, был добавлен сигнал QDS, который располагается на печатной плате вместе с линиями данных. По нему происходит синхронизация при передаче данных. Если используется два модуля памяти, то данные от них приходят к контроллеру памяти с небольшой разницей из-за разного расстояния. Возникает проблема в выборе синхросигнала для их считывания и использование QDS успешно это решает.

JEDEC устанавливает стандарты для скоростей DDR SDRAM, разделённых на две части: первая для чипов памяти, а вторая для модулей памяти, на которых, собственно, и размещаются чипы памяти.

Чипы памяти.

В состав каждого модуля DDR SDRAM входит несколько идентичных чипов DDR SDRAM. Для модулей без коррекции ошибок (ECC) их количество кратно 8, для модулей с ECC — кратно 9.

Спецификация чипов памяти:

- DDR200: память типа DDR SDRAM, работающая на частоте 100 МГц. МГц. МГц. МГц. МГц. МГц. МГц.

- DDR266: память типа DDR SDRAM, работающая на частоте 133

- DDR333: память типа DDR SDRAM, работающая на частоте 166

- DDR400: память типа DDR SDRAM, работающая на частоте 200

- DDR533: память типа DDR SDRAM, работающая на частоте 266

- DDR666: память типа DDR SDRAM, работающая на частоте 333

- DDR800: память типа DDR SDRAM, работающая на частоте 400

Характеристики чипов:

Объём чипа (DRAM density). Записывается в мегабитах, например 256 Мбит — чип объёмом 32 мегабайта.

Организация (DRAM organization). Записывается в виде 64M x 4, где 64M — это количество элементарных ячеек хранения (64 миллиона), а x4 (произносится «by four») — разрядность чипа, то есть разрядность каждой ячейки. Чипы DDR бывают x4 и x8, последние стоят дешевле в пересчёте на мегабайт объёма, но не позволяют использовать функции Chipkill, memory scrubbing и Intel SDDC.

Модули памяти:

Модули DDR SDRAM выполнены в форм-факторе DIMM. На каждом модуле расположено несколько одинаковых чипов памяти и конфигурационный чип SPD. На модулях регистровой (registered) памяти также располагаются регистровые чипы, буферизующие и усиливающие сигнал на шине, на модулях нерегистровой (небуферизованной, unbuffered) памяти их нет.

Характеристики модулей:

-

- Объём. Указывается в мегабайтах или гигабайтах.

- Количество чипов (# of DRAM Devices). Кратно 8 для модулей без ECC, для модулей с ECC — кратно 9. Чипы могут располагаться на одной или обеих сторонах модуля. Максимальное умещающееся на DIMM количество — 36 (9×4).

- Количество строк (ранков) (# of DRAM rows (ranks)). Перед обращением к ячейке памяти DDR должна быть активирована строка, в которой находится эта ячейка, причём в модуле может быть активна только одна строка за раз. Чем больше строк в модуле, тем чаще в среднем придётся закрывать одну строку и активировать другую, что вызовет дополнительные задержки. С другой стороны, контроллер памяти некоторых чипсетов имеют ограничение на общее число ранков в установленных модулях памяти. Например чипсет Intel E7520/E7320 при использовании памяти PC2700 ограничен 8 ранками. Чтобы установить в материнскую плату на его основе с 8 слотами DIMM максимум памяти (2 Гб x 8 = 16 Гб), необходимо использовать только одноранковые (Single Rank) модули. Типичное число ранков — 1, 2 или 4. Разрядность строки равна разрядности шины памяти и составляет 64 бита для памяти без ECC и 72 бита для памяти с ECC.

- Задержки (тайминги): CAS Latency (CL), Clock Cycle Time (tCK), Row Cycle Time (tRC), Refresh Row Cycle Time (tRFC), Row Active Time (tRAS).

Характеристики модулей и чипов, из которых они состоят, связаны.

Объём модуля равен произведению объёма одного чипа на число чипов. При использовании ECC это число дополнительно умножается на коэффициент 8/9, так как на каждый байт приходится один бит избыточности для контроля ошибок. Таким образом один и тот же объём модуля памяти можно набрать большим числом (36) маленьких чипов или малым числом (9) чипов большего объёма.

Общая разрядность модуля равна произведению разрядности одного чипа на число чипов и равна произведению числа ранков на 64 (72) бита. Таким образом, увеличение числа чипов или использование чипов x8 вместо x4 ведёт к увеличению числа ранков модуля.

Спецификация модулей памяти.

DDR2 SDRAM пришла на смену памяти типа DDR SDRAM.

Как и DDR SDRAM, DDR2 SDRAM использует передачу данных по обоим срезам тактового сигнала, за счёт чего при такой же частоте шины памяти, как и в обычной SDRAM, можно фактически удвоить скорость передачи данных (например, при работе DDR2 на частоте 100 МГц эквивалентная эффективная частота для SDRAM получается 200 МГц). Основное отличие DDR2 от DDR — вдвое большая частота работы шины, по которой данные передаются в буфер микросхемы памяти. При этом чтобы обеспечить необходимый поток данных, передача на шину осуществляется из четырёх мест одновременно. Итоговые задержки оказываются выше, чем для DDR.

Описание:

Внешнее отличие — 240 контактов (по 120 с каждой стороны). Микросхемы памяти DDR2 производятся в новом корпусе типа BGA (FBGA).

Напряжение питания микросхем 1,8 В. Потребляемая мощность: 247 мВт.

Интерфейс ввода-вывода: SSTL_18. Burst Length: 4/8.

Prefetch Size: 4-bit.

Новые функции: ODT, OCD Calibration, Posted CAS, AL (Additive Latency).

Спецификация чипов памяти:

Тип чипа Частота памяти Частота шины Передач данных в секунду:

- DDR2-400 100 МГц 200 МГц 400 млн.

- DDR2-533 133 МГц 266 МГц 533 млн.

- DDR2-667 166 МГц 333 МГц 667 млн.

- DDR2-800 200 МГц 400 МГц 800 млн.

- DDR2-1066 266 МГц 533 МГц 1066 млн.

Спецификация модулей памяти.

DDR3 SDRAM пришла на смену памяти типа DDR2 SDRAM.

Возможности микросхем DDR3 SDRAM.

- Предвыборка 8 бит.

- Функция асинхронного сброса с отдельным контактом.

- Поддержка компенсации времени готовности на системном уровне.

- Зеркальное расположение контактов, удобное для сборки модулей.

- Выполнение CAS Write Latency за такт.

- Встроенная терминация данных.

- Встроенная калибровка ввода/вывода (мониторинг времени готовности и корректировка уровней).

- Автоматическая калибровка шины данных.

Возможности модулей DIMM DDR3.

- Последовательная топология управляющей шины (управление, команды, адреса) с внутримодульной терминацией.

- Высокоточные резисторы в цепях калибровки.

Преимущества по сравнению с DDR2.

- Более высокая полоса пропускания (до 2400 МГц).

- Сниженное тепловыделение (результат уменьшения напряжения питания).

- Меньшее энергопотребление и улучшенное энергосбережение.

Недостатки по сравнению с DDR2.

- Более высокая CAS-латентность (компенсируется большей пропускной способностью).

- CAS-латентность (англ. column address strobe latency) — это время (в циклах) ожидания между запросом процессора на получение ячейки с информацией из памяти и временем, когда оперативная память сделает доступным для чтения первую ячейку.

Спецификация модулей памяти.

Модули памяти SDR SDRAM могут иметь CAS-латентность, равную 1, 2 или 3 циклам. Модули DDR SDRAM могут иметь CAS- латентность, равную 2 или 2.5.

На модулях памяти CAS-латентность обозначается как CAS или CL. Пометка CAS2, CAS-2, CAS=2, CL2, CL-2 или CL=2 обозначает величину латентности, равную 2.

Особенности архитектуры памяти.

Коррекция ошибок.

Выявление и исправление ошибок (ЕСС — Error Checking and Correction) — этот специальный алгоритм, который заменил контроль четности в современных модулях памяти. Каждый бит данных включается более чем в одну контрольную сумму, поэтому при возникновении в нем ошибки возможно восстановить адрес и исправить сбойный бит. При сбоев двух и более битах ошибка лишь фиксируется, но не исправляется.

Система адресации.

Для адресации ячеек памяти используют особенности матричной структуры. Полный адрес ячейки состоит из адресов строки и столбца. Для считывания (записи) информации на микросхему сначала подается сигнал RAS (Row Actress Strobe — импульс доступа к строке), а затем (одновременно или с небольшой задержкой) — код адреса строки. После этого через нормируемое время задержки должен быть подан код адреса столбца, перед которым проходит сигнал CAS (Column Adress Strobe — импульс доступа к столбцу). Под временем выборки микросхемы подразумевают промежуток между сигналами RAS. Следующее обращение к памяти возможно только через некоторое время, необходимое для восстановления внутренних/цепей. Этот промежуток называют временем перезарядки, причем оно составляет почти 90% от общего времени выборки. Данные из ячеек через усилители поступают в регистр микросхемы, откуда они становятся доступными после открытия линии DOUT (Data OUT). При операциях записи данные поступают по линии DIN (Data IN), а цикл происходит в обратном порядке.

Любое системное устройство, обладающее правом прямого доступа к памяти (по одному из каналов DMA — Direct Memory Acces), при необходимости посылает запрос, содержащий адрес и размер блока данных, а также управляющие сигналы.

Так как доступ к памяти по каналам DMA одновременно могут иметь несколько устройств (например, процессор, видеокарта с интерфейсом AGP, контроллер шины PCI, жесткий диск), образуется очередь запросов, хотя каждому потребителю ресурсов памяти требуются собственные данные, часто расположенные не только в разных микросхемах, но и в разных банках памяти. Тем самым образуются значительные задержки при получении/записи данных. Технологии, позволяющие снизить или обойти перечисленные ограничения, описаны ниже.

Тайминг.

Время пересылки данных измеряют в тактах микропроцессора и обычно записывают так: 6-2-2-2. Это означает, что на первую пересылку данных из произвольный ячейки памяти потребовалось 6 тактов шины, а на все последующие ячейки — по 2. Синхронная память обычно превосходит по быстродействию асинхронную. Например, при частоте системной шины 66 МГц память типа EDO 60 нc работает по схеме 5-2- 2-2, а память типа SDRAM 10 нc, по схеме 5-1-1-1, что теоретически дает выигрыш в производительности около 30%.

На практике преимущество SDRAM меньше примерно на порядок, потому что далеко не все данные представляют собой последовательную выборку. Но уже при частоте системной шины 100 МГц память EDO 60 нc неработоспособна, a SDRAM 10 нc продолжает работу по схеме 5-1-1- 1.

REPORT THIS AD.

Производители и маркировка модулей памяти.

Для ориентировки приводим буквенный префикс обозначения продукции известных фирм, относящихся к группе major- производителей.

Fujitsu — MB; Hyundai — НУ;

LG Semicon — GM; Mitsubishi — M5M; NEC — mPd;

Samsung — KM;

Texas Instruments — TMS; Hitachi — HB;

IBM — IBM;

Micron — MT; Mosel Vitelic — V; Oki — MSM;

Siemens — HYB;

Toshiba — TC.

Альтернативная и перспективная память:

DDR4, SL DRAM,VCM DRAM, ESDRAM, FCRAM, FeRAM, MRAM.